From Models to Systems: GO HW for Unified AI and Hardware Execution

## **Table of Contents**

| ٧ | ersioning                                                                                               | 3  |

|---|---------------------------------------------------------------------------------------------------------|----|

| E | xecutive Summary                                                                                        | 4  |

| F | rom a static file to a living graph                                                                     | 5  |

|   | ONNX in plain language                                                                                  | 5  |

|   | ONNX Runtime in practice                                                                                | 6  |

|   | Compiler strategy: IR-last today, IR-first optional tomorrow                                            | 7  |

| G | raph computing as a quiet revolution                                                                    | 8  |

|   | Back to the 80s, NI and the birth of LabVIEW                                                            | 9  |

|   | Graiphic chapter 1 — A Keras style toolkit that hit two walls                                           | 10 |

|   | Graiphic chapter 2 — one file, one engine, one cockpit                                                  | 11 |

|   | From inference to training and orchestration, still a graph                                             | 14 |

|   | The NI Connect moment                                                                                   | 15 |

| S | oC basics without the jargon                                                                            | 16 |

| S | tate of the Art in Graph Computing and Hardware Orchestration (2021–2025)                               | 17 |

|   | Introduction                                                                                            | 17 |

|   | Graph Compilers and Runtimes                                                                            | 18 |

|   | Pipeline Orchestration Frameworks                                                                       | 18 |

|   | Hardware-Specific SDKs and DSLs                                                                         | 19 |

|   | Limitations of the Current State of the Art                                                             | 19 |

|   | Transition to GO HW                                                                                     | 19 |

|   | Comparative Snapshot                                                                                    | 20 |

|   | Closing Sentence                                                                                        | 20 |

| G | O HW, a concrete path from static description to dynamic technology                                     | 20 |

|   | GO HW on SoCs, author, configure, deploy, monitor                                                       | 21 |

|   | Energy-Aware Graphs and Forensic Monitoring                                                             | 24 |

|   | LabVIEW-native forensic measurement                                                                     | 25 |

|   | Open benchmarking and transparent culture                                                               | 25 |

|   | Algorithmic Enhancements: Dynamic Loss Functions and Informed Learning through Full Graph Orchestration |    |

|   | Dynamic, energy-aware loss design.                                                                      | 26 |

|   | Graph-compilation efficiency as orchestration property.                                                 | 26 |

#### **∳**GRAIPHIC

| Integration of alternative learning paradigms                                               | 26 |

|---------------------------------------------------------------------------------------------|----|

| Impact: Green AI by design                                                                  | 27 |

| Energy-aware contributions of SOTA and GO HW                                                | 27 |

| Closing, one graph, many roles                                                              | 28 |

| Implementation and Deployment of ONNX GO HW on SoCs (Raspberry Pi 5 as First<br>Case Study) | 29 |

| Proposed Path Forward for ONNX steering committee                                           | 34 |

| Why ONNX Needs a Hardware Working Group, Strategic Rationale                                | 35 |

| Target platform matrix for GO HW v1.0                                                       | 39 |

| Frequently Asked Questions (FAQ)                                                            | 40 |

| Call for Funding: Why Industry Should Invest in GO HW                                       | 42 |

| Annexes                                                                                     | 43 |

| Support Letters                                                                             | 43 |

| Graph Computing for AI Systems: State-of-the-Art (2021–2025)                                | 45 |

| Introduction                                                                                | 45 |

| Academic Advances in Graph Computing (2021–2025)                                            | 45 |

| Industrial Frameworks and Ecosystems                                                        | 47 |

| Toward Unified Graph Orchestration: ONNX GO HW vs. Existing Solutions                       | 51 |

## Versioning

This document is subject to version control to ensure full traceability of changes. Each update is recorded with its author, date, and a short description of the modifications.

| Version | Date       | Author          | Organization | Change Description                           |

|---------|------------|-----------------|--------------|----------------------------------------------|

| 1.0     | 2025/08/31 | Youssef Menjour | Graiphic     | First publication of the GO HW<br>Whitepaper |

| 1.1     | 2025/09/04 | Youssef Menjour | Graiphic     | No SONNX                                     |

| 1.2     | 2025/09/11 | Youssef Menjour | Graiphic     | FAQ update                                   |

| 1.3     | 2025/09/18 | Youssef Menjour | Graiphic     | IR First / Last                              |

## **Executive Summary**

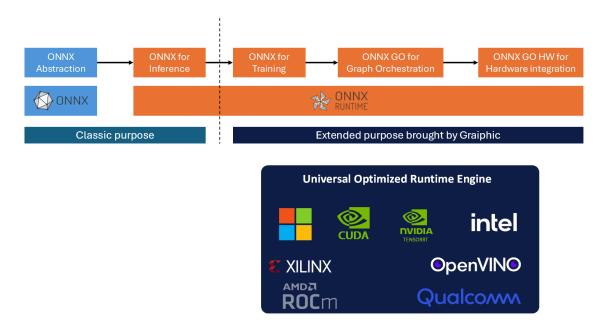

ONNX has established itself as the de facto standard for portable AI inference, allowing models to run efficiently across CPUs, GPUs, FPGAs and NPUs. Graiphic's work builds directly on this foundation and extends ONNX into a much broader role: not only a format for inference, but a complete framework for orchestrating AI, logic and hardware in a unified and transparent way.

This evolution has unfolded in three major steps. First, we enabled training workflows inside ONNX, combined with LabVIEW orchestration, which are already used in Graiphic's Deep Learning Toolkit. Second, we introduced ONNX GO, an orchestration layer that supports control structures such as conditionals, loops and runtime branching, and which is already deployed in the LabVIEW Accelerator Toolkit. The third step, which this document focuses on, is ONNX GO HW: a new layer that integrates hardware primitives such as DMA transfers, GPIO, ADC/DAC and timers directly into ONNX graphs.

The goal of ONNX GO HW is to make hardware orchestration as seamless and standardized as AI inference itself. The analogy with NI's DAQmx is intentional: just as DAQmx unified hardware configuration and access through a single interface, ONNX GO HW provides an open and portable representation of hardware tasks that can be defined and scheduled inside ONNX graphs. Unlike DAQmx, this approach is not tied to proprietary APIs or devices but remains compatible across multiple runtimes and platforms.

LabVIEW plays a central role as the natural cockpit for this technology. Engineers can visually design, deploy and monitor systems that combine artificial intelligence with real-world hardware control, all within a single workflow. This creates a powerful bridge between abstract AI models and physical systems, with immediate benefits in test and measurement, robotics, industrial automation, aerospace and defense.

ONNX GO HW introduces a new paradigm in execution. By embedding hardware orchestration into standardized graphs, it transforms ONNX from a static description of models into a dynamic and auditable framework capable of managing the entire lifecycle of intelligent systems.

## From a static file to a living graph

**Every ONNX model is a little play**. The cast are nodes, the props are tensors, and the script is the graph. Most of us only hire the math stars that do convolutions, matmuls, and activations. Three quiet actors wait in the wings: If, Loop, and Scan. They rarely get called when we only do classic deep learning inference, yet they hold the keys to choreography. With them, a graph can describe not just what to compute, but when to compute and how often to repeat. That is where the story gets interesting.

We call this idea GO, for graph orchestration. GO is the goal of turning ONNX from a static description into a dynamic technology. The artifact stays the same, yet the way we use it changes. ONNX brings a universal, interoperable format. ONNX Runtime brings an efficient execution engine. Together they already run fast on many targets. With GO, the graph also carries schedules and control flow in a first-class way, so you coordinate learning loops, evaluation passes, and model lifecycle without leaving the ONNX world.

There is a catch. ONNX today shines as a file format and as a runtime target, yet it lacks a native editor. You can convert from popular frameworks, you can execute with ONNX Runtime, but you cannot comfortably import, edit, and create ONNX graphs without going back to third party toolchains. That dependency keeps ONNX as an excellent tool, not yet a complete graph computing framework. It slows innovation because the ideas must pass through a different language before they become ONNX.

This is the gap Graiphic is closing. We keep ONNX as the single source of truth, expose both levels of abstraction, and make the control flow nodes easy to use. Engineers can work at a Keras style layer level. Researchers can sculpt at the node level. Everyone edits the same graph, saves the same format, and benefits from the same runtime.

## ONNX in plain language

Before we orchestrate anything, let us make the building blocks feel familiar. ONNX is an open way to write a computation as a graph. A node is an operation. An edge carries a tensor from one node to the next. Some tensors are not inputs at all but weights stored inside the model. Each node has attributes that set its behavior, for example a kernel size or an activation choice. Put these pieces together and you have a recipe the computer can follow step by step.

**Think of ONNX as sheet music**. The notes are operations like MatMul, Conv, Add, Relu. The bars are tensors that flow across the page. The tempo is set by shapes and types that tell the runtime how large the arrays are and how they line up in memory. A model file simply packages the score with its instruments. It contains the graph, the weights, the operator set version, and a little metadata such as names and documentation. You can pass this file between tools and keep meaning intact.

Why is this useful beyond conversion? Because a graph is precise and inspectable. You can open it, count the tensors, check the shapes, and see exactly how data moves. You can split it in two, reuse a prefix, or swap a small part without touching the rest. You can

run it on a laptop, a workstation, or a small board and expect the same logical behavior. When a team says one source of truth, this is what they mean.

If, Loop, and Scan enable control flow inside the graph, essential for orchestration and training logic. They're already part of ONNX and will be key to express full execution schedules. If choose a path based on a condition. Loop repeats a subgraph and carries state across steps. Scan walks over a sequence and collects results. Most people ignore them when they only deploy a fixed network, yet they make the format future ready. They are the handles we will use later to express schedules and learning cycles inside the same artifact.

A final detail completes the picture. ONNX is neutral about taste. It does not force a style like layers only or operators only. You can treat the graph as a high-level model if that is the right abstraction for an engineer, or you can treat it as a set of fine-grained operators if you are a researcher crafting something bespoke. The file does not change, only the editor you prefer.

#### Cheat sheet

- Node: a single operation that consumes and produces tensors

- Tensor: an array with a shape and a data type

- Initializer: a tensor stored in the model, usually a weight

- Attribute: a small setting attached to a node

- Opset: the versioned catalog of available operators

### **ONNX** Runtime in practice

Now that the score is clear, meet the conductor. ONNX Runtime reads the graph, plans the work, and plays it efficiently on real hardware. It chooses kernels, arranges memory so tensors land where they should, and removes extra steps by fusing compatible nodes. The result is a compiled session that you can call many times with stable latency and a predictable footprint.

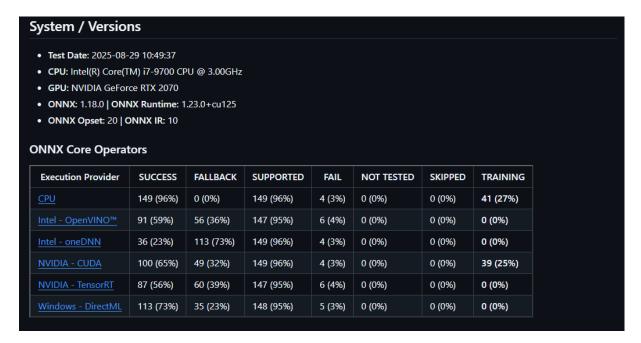

Think of execution as a three-part routine. First comes analysis. The runtime checks shapes and data types, folds constants, and prunes dead branches. Second comes partitioning. Subgraphs are assigned to Execution Providers that know how to run them fast, for example above the native CPU, CUDA and TensorRT for NVIDIA, oneDNN and OpenVINO for Intel, ROCm and VitisAI for AMD, and DirectML for Windows GPUs. Third comes scheduling. The runtime builds an execution plan that minimizes copies, aligns layouts, and reuses memory arenas so nothing is allocated in the hot path.

A useful detail is that the graph stays the source of truth. You can inspect the optimized graph, see which parts got fused, and verify exactly which provider runs which segment. If a device is missing, the same artifact still runs on a plain CPU provider with the same logical behavior, just at a different speed, that's what we call the Fallback mechanism. This keeps experiments honest and production portable.

Here is a simple way to place ONNX Runtime in your mental map.

#### Library vs runtime, in one glance

- A library gives you individual operations such as MatMul or Conv (examples: CUDA, OneDNN, RocM, DirectML)

- A runtime takes a whole graph, compiles it end to end, and decides how and where to run each part (examples: TensorRT, OpenVINO Runtime, VitisAI Runtime, ONNX Runtime)

- Libraries are the instruments, the runtime is the conductor

- ONNX Runtime integrates with many runtimes and libraries via Execution Providers and falls back to the CPU provider when needed

Two side effects matter in practice. Efficiency improves because the runtime can fuse chains of operations and keep data in the right format between them. Energy improves because fewer copies and fewer cache misses translate into less wasted work. Both effects show up the moment you repeat inference at scale.

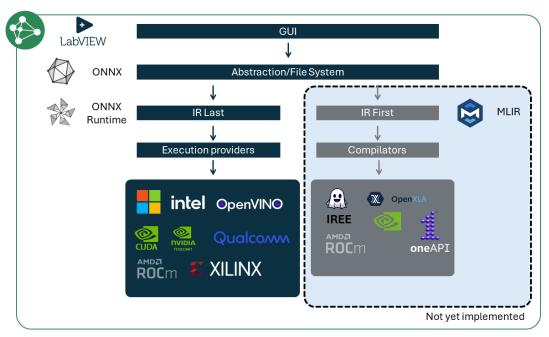

#### Compiler strategy: IR-last today, IR-first optional tomorrow.

An Intermediate Representation (IR) is the neutral "sheet music" of a program that enables analysis, optimization, and lowering to hardware. Today we favor an IR-last path with ONNX Runtime: the ONNX graph remains the source of truth while the runtime performs graph-level optimizations and partitions subgraphs to hardware Execution Providers (TensorRT, OpenVINO, DirectML, ROCm, ...). This maximizes portability, coverage, and time-to-first-inference. In parallel, we open an IR-first lane with MLIR: models are lowered through dialects (e.g., ONNX or StableHLO) and compiled end-to-end (e.g., via IREE or OpenXLA) for ahead-of-time specialization, tight latency budgets, and target-specific scheduling. Bridges (ONNX-MLIR, StableHLO) make both lanes interoperable. Net effect: under the same LabVIEW GUI and orchestration, users can pick runtime breadth (IR-last) or compiler-grade specialization (IR-first) per deployment.

Dual IR Strategy — ORT (IR-last) vs MLIR (IR-first) under LabVIEW Orchestration

Graiphic deliberately starts with an **IR-last** path built on **ONNX Runtime**: the ONNX file remains the single source of truth, while the runtime performs graph-level optimizations and **partitions subgraphs to hardware Execution Providers** before scheduling them efficiently. This maximizes portability, coverage, and time-to-first-inference. Next, we will expose an **optional IR-first lane** based on **MLIR** (e.g., IREE/OpenXLA). When targets or workloads benefit from ahead-of-time specialization, static-shape lowering, or custom dialects, the same ONNX graph can be lowered to MLIR dialects and compiled end-to-end to native executables. **Users will choose per deployment** between the ORT path (EPdriven runtime) and the MLIR path (compiler pipeline), under the same LabVIEW cockpit, device profiles, and monitoring plane. This dual strategy keeps our **portability-first** promise while opening the door to **compiler-grade determinism and specialization** where it matters.

## Graph computing as a quiet revolution

Once you see a model as a graph, you start seeing most workflows as graphs. A graph is a contract that lists the steps, the data that flows between them, and the rules that govern the journey. It is transparent, easy to inspect, and easy to test. You can run a single subgraph to debug an issue, then run the full plan with the confidence that the behavior will match. This mindset turns scattered scripts into a single artifact that you can reason about.

With If, Loop, and Scan, graphs can carry full training, evaluation, and control loops — all in a reproducible, inspectable way.

Graphs also make optimization a first-class activity. Because the plan is explicit, a runtime can fuse operations, reuse buffers, and select precisions that fit the budget. Because the plan is versioned, a team can review changes, compare metrics, and roll back without guessing which script or notebook drifted. Provenance stops being a headache and turns into a property of the file.

This is why we describe GO as **g**raph **o**rchestration. The idea is simple. Keep one artifact. Put both computation and schedule inside it. Let the runtime turn that plan into an execution that is fast and predictable on real machines. You gain portability, you gain performance, and you gain a common language between engineers and researchers.

#### Micro checklist for graph ready work

- Preprocessing and metrics belong in the graph when possible

- Control flow is explicit, not hidden in outer scripts

- Seeds, shapes, and dtypes are recorded for reproducibility

- Subgraphs are modular so teams can reuse and swap them

- The optimized graph is inspected like code

If graphs make complex systems visible, LabVIEW proved it decades ago by turning dataflow into an everyday tool for engineers. Let us rewind to see why that matters now.

#### Back to the 80s, NI and the birth of LabVIEW

**Picture the mid-Eighties**. Personal computers get a proper graphical interface. Engineers want instruments to talk to software without wrestling with arcane drivers. National

Instruments sells the boards and sees the gap. In Austin, three engineers, James Truchard, Jeff Kodosky, and Bill Nowlin, have already founded National Instruments in 1976 with a simple focus: connect instruments to computers so that scientists and engineers can get results faster. Early products revolve around GPIB and measurement cards, yet the deeper ambition is to make the computer feel like an instrument that you can compose and recompose at will.

James Truchard, Jeff Kodosky and Bill Nowlin

LabVIEW While Loop abstraction within it's diagram IDE

Jeff Kodosky has a simple question that sounds audacious in that context. What if programming for measurement and control looked like drawing a circuit that runs?

LabVIEW is the answer. The front panel is where you place knobs, charts, and indicators. The block diagram is where you wire boxes that do work. Data flows along wires and triggers execution when inputs are ready. The result feels like an oscilloscope pointed at your own program. You click run and watch

values ripple through the graph in real time. You correct mistakes by looking, not guessing.

As LabVIEW made dataflow tangible, NI solved the other half of the problem with a unified driver stack: NI-DAQmx. Instead of coding per-board quirks, engineers declared what they wanted, sample clock, channel list, trigger, buffer size and DAQmx handled how to talk to multiplexed ADCs, counters, timers and DMA behind the scenes. Critically, the DAQmx task model mapped cleanly to LabVIEW's block diagram: configure once, start, read/write, stop, with deterministic timing and good diagnostics. That pairing "visual dataflow + a portable hardware abstraction" is the historical proof that orchestration and I/O can live in one mental model. GO HW borrows that lesson: keep the graph as the plan, keep a clean runtime, and expose hardware primitives as first-class nodes instead of adhoc glue.

Control is part of the picture from day one. If, For, and While sit beside math nodes and filters. They let you express choices, loops, and orderly repetition with the same visual

clarity. The idea is not to hide complexity. The idea is to make it visible so teams can reason about behavior, timing, and state without reading a wall of text.

Why does this matter to our story about ONNX. Because it proves that graphs are a practical way to build and operate complex systems. It shows that an IDE can help non-specialists work confidently with powerful machinery when the model of computation matches how they think. It also shows that orchestration is not a footnote. It is the method that turns a collection of operations into a working system.

#### LabVIEW in one minute

- **1986**

- Pioneered the industrial application of graph computing through LabVIEW Visual dataflow, not syntax rules

- Two synchronized views, front panel and block diagram

- Live execution, you can watch and debug

- Control structures that make behavior explicit

That same clarity is what we wanted for modern AI workflows, which led to our first toolkit and the lessons that shaped the pivot.

#### Graiphic chapter 1 — A Keras style toolkit that hit two walls

HAIBAL (2022), Our first LabVIEW deep learning toolkit spoke fluent Keras. It offered layers you could stack, an H5 file you could save, and a clean mental model that many engineers already knew. That choice made adoption easy, yet it hid a mismatch. Keras layers are friendly abstractions, while ONNX and modern runtimes reason in finer grained nodes. PyTorch and TensorFlow can export models as operator level graphs. Our layer centric design could not round trip neatly with that world. Converters had to guess how a stack of layers mapped to a set of low-level ops. Small gaps turned into friction.

The second wall was speed. We executed through the LabVIEW runtime with a light CUDA bridge. It worked and it was ergonomic, but it was not built for the scale and cadence of tensor compute. The hot path did too many small calls. Memory moved more than it should. Kernels could not fuse across the layer boundaries we had chosen. When we compared common models with mainstream frameworks, we saw the gap in latency and throughput.

**Both walls taught the same lesson**. The file format and the execution engine must sit at the center. An editor that feels good is not enough if the artifact is not native to the ecosystem you target. A runtime that feels integrated is not enough if it cannot plan whole graphs and keep the hot path tight. We needed to keep the ergonomics of layers for engineers, open the door to node level editing for researchers, and anchor the truth in an ONNX file that any tool could read.

#### What we kept and what we changed

- Kept the clarity of layers for quick prototyping

- Added node level access for custom research work

- Replaced H5 as the primary artifact with ONNX as the single source of truth

- Moved execution from the LabVIEW runtime to an engine built for graphs

#### Graiphic chapter 2 — one file, one engine, one cockpit

Editors change, hardware changes, teams change. The artifact stays the same and the engine keeps it honest.

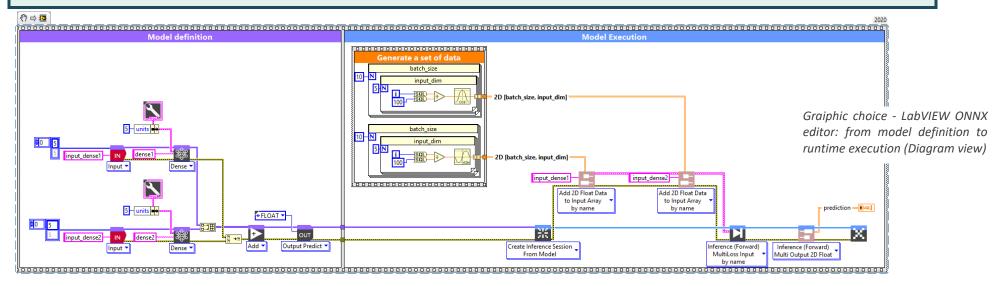

We support two lanes without splitting the road. In layer mode an engineer builds with friendly blocks that feel like Keras. In node mode a researcher edits fine grained operators and custom subgraphs. Both lanes write to the same ONNX graph, with the same shapes, the same weights, the same metadata. You can start in layers for speed, drop to nodes for precision, and never leave the file that ships.

Performance stops being an accident and becomes a property of the build. ONNX Runtime compiles the graph into a session, fuses compatible chains, allocates memory arenas, and plans formats so tensors do not bounce around. You call the session many times with the same inputs, and the hot path stays tight. Latency becomes predictable, throughput scales, energy stops leaking into copies you did not ask for.

The day-to-day experience improves too. The ONNX file is versioned like code. Diffs are meaningful because the graph is declarative. Tests can run on a CPU provider during development and switch to an accelerator provider in staging with the same logical behavior. When something regresses, you inspect the optimized graph and see what changed rather than guess which script drifted.

Graiphic did not approach ONNX as a fixed standard limited to Al inference. From the beginning, we considered ONNX as a foundation for a broader category of graph-based execution systems. This perspective led to a series of structured extensions and contributions that progressively expanded the ONNX Runtime ecosystem.

#### **∳**GRAIPHIC

The first breakthrough was the integration of training workflows directly into ONNX graphs. Through our internal platform SOTA, we demonstrated that neural network training, including backpropagation, could be described and executed within ONNX Runtime. This eliminated the need for Python training loops or external scripting, proving that ONNX could support dynamic learning operations rather than being limited to static inference.

ONNX Evolution: From AI Inference to Full Graph-Based System Orchestration

Building on this foundation, we introduced ONNX GO, a framework for Graph Orchestration. ONNX GO extended the ONNX specification with control flow constructs such as conditional branching (If), iteration (Loop), and structured scans (Scan). These additions allowed ONNX graphs to express general-purpose logic, including decision trees, processing pipelines, and reactive system behaviors.

To make these capabilities accessible, we integrated ONNX GO into LabVIEW, creating a visual environment for graph composition and execution. Engineers could now design, modify, and run ONNX-based systems across various platforms using a graphical interface that supports modularity, clarity, and live debugging.

This progression from inference, to training, to full orchestration laid the groundwork for the next step. ONNX GO HW emerged as a natural extension, introducing hardware-level access as a native part of ONNX graphs. It completes the transformation of ONNX into a universal execution layer capable of describing both software logic and physical hardware control in a single, portable format.

A small quality of life loop closes the circle. Import a legacy model, normalize it to a clean ONNX graph, run quick shape checks, auto generate minimal docs from operator metadata, and compile a warm session for your target. The file becomes the contract. The runtime becomes the guarantee.

#### Rules of engagement

- One ONNX bundle is the source of truth for models and transforms

- Treat layer mode as a convenience, not a trap

- Keep pre and post processing in the graph when possible

- Inspect the optimized graph like you review code

- Compile once per target for stable memory and timing

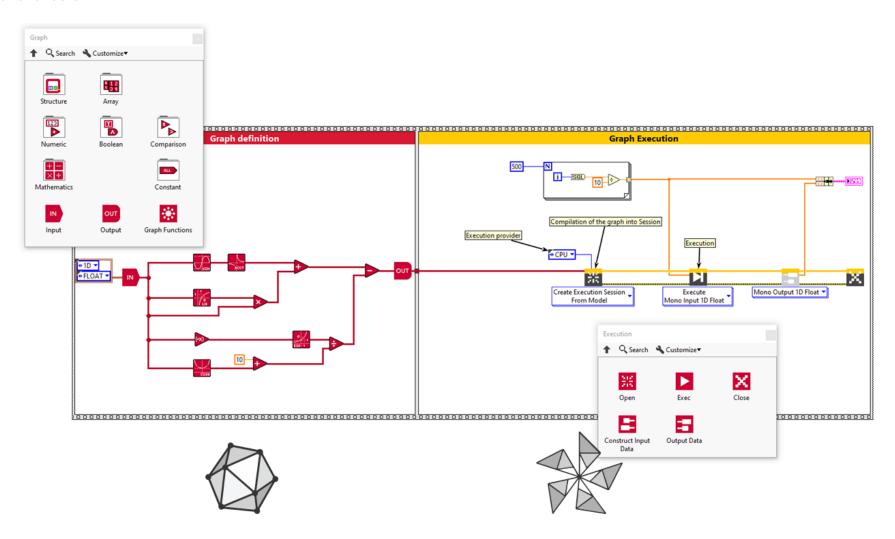

The editor reads left to right. In the purple area "Model definition" you build the ONNX graph with blocks (Inputs, Dense, Add, Output) and keep a clean ONNX artifact. In the blue area "Model Execution" you open an ONNX Runtime session from that model, inject batched inputs, run the forward pass, and collect the outputs. The same ONNX file drives both validation and execution; only the view changes from authoring to running.

Graphs made complex systems visible. The next step is to let the same graph do more than predict. From inference to training and orchestration, it is still a graph.

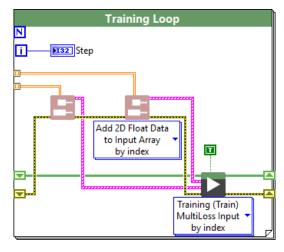

## From inference to training and orchestration, still a graph

We keep one artifact, the ONNX graph, and we teach it new moves. Conceptually a training graph adds a loss, gradients, and an optimizer to the forward path. These pieces fit the ONNX mindset and keep the artifact versionable and auditable. They make training a plan you can read instead of a pile of scripts.

LabVIEW ONNX editor: Palette

Here is the practical nuance in our current stack.

Today the **orchestration loop lives in LabVIEW**, not inside the ONNX graph. LabVIEW plays the role of If, Loop, and Scan in its own dataflow. We tick the loop, feed inputs to the graph, run one forward pass, collect outputs, and repeat. This keeps high level control familiar and debuggable while we gradually move schedule logic into ONNX when it is mature enough. The diagrams you shared show this clearly. The model is defined once, a session is created, and LabVIEW drives the sequence one inference at a time.

We support three session flavors in ONNX Runtime so teams choose the right granularity without changing tools:

- Inference session Classic forward only. Use for serving and evaluation.

- **Training session** in fit mode (green wires) Forward, loss, backward, and update handled as a single callable.

- Academic session Forward and backward are exposed separately so you can inspect tensors, plug custom losses, or prototype research ideas.

LabVIEW Diagram Orchestration of ONNX Runtime Training Inference

LabVIEW Training Inference functionality

This hybrid phase is intentional. It delivers value now and sets a clean path to full in graph orchestration later. You already get compiled sessions, fused kernels, and stable memory on each target. You already keep preprocessing and metrics close to the model so runs are reproducible. You already ship a single ONNX file that moves from experiment

to evaluation to serving. What changes next is where the schedule lives. We will gradually

encode epoch loops, mini batch steps, and early stopping with ONNX control flow so the artifact carries both computation and cadence.

#### Micro callout

- Today: LabVIEW owns the loop and calls ONNX Runtime each tick

- Tomorrow: control flow migrates into ONNX using If, Loop, and Scan

- Always: one ONNX file, one compiled session per target, the same truth in every phase

#### The NI Connect moment

We arrived at NI Connect with one story to tell. A clean LabVIEW experience on top of ONNX and ONNX Runtime for deep learning, with the orchestration loop living in LabVIEW. The first discussion with NI engineers changed the scope in the best possible way. If the graph can express complex deep learning, it can also express simpler building blocks from the LabVIEW palette. That idea kicked off the Accelerator Toolkit. The goal was straightforward. Generalize ONNX beyond deep learning and use ONNX Runtime to execute any compute graph efficiently.

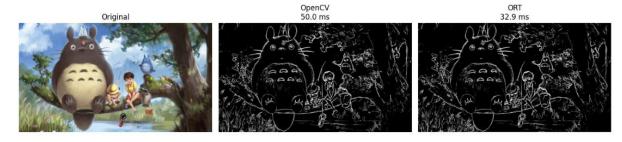

Results followed quickly. A matrix multiplication benchmark on CPU showed the Accelerator beating native LabVIEW by a wide margin. At size 8000 the time ratio reached about 5.5 in our test VI, with ten iterations per size for fair timing. The same pattern appeared in computer vision. A Sobel edge detector built as an ONNX graph and run with ONNX Runtime outpaced an OpenCV implementation by roughly 30 to 40 percent depending on resolution. These two measurements gave us confidence that the generalized graph route was sound. The videos and screenshots we shared with NI captured the effect clearly.

Comparison between OpenCV and ONNX runtime time execution performance on Sobel Edge Detector on an CPU execution provider (ORT: ONNX Runtime)

The second moment came the next day with an NI engineer who had missed the first meeting. Your idea to generalize graphs is good, he said, but how do you control hardware signals with this technology. The question landed and stayed. It reframed the problem from pure acceleration to timing and alignment with the real world.

The timeline matters. In May we had only the deep learning toolkit and a LabVIEW driven loop that fed the graph and called ONNX Runtime step by step. In July we shipped the Accelerator Toolkit to prove that generalized graphs run fast for pre and post processing and for standalone math. In August we began shaping the hardware path. The order is

deliberate. Show speed first, then bring timing into focus, then extend the model to the physical layer. Step by step.

Two ideas were born in those conversations with NI. First, treat ONNX as a general graph that can execute efficiently beyond deep learning. Second, answer the hardware question with a design that makes timing and control as explicit as the math. The first idea is already in the product. The second is the seed we are growing now.

Generalizing the graph is only half the story. To act on the physical world, we need to speak the language of chips. A short tour of SoCs makes the stakes concrete.

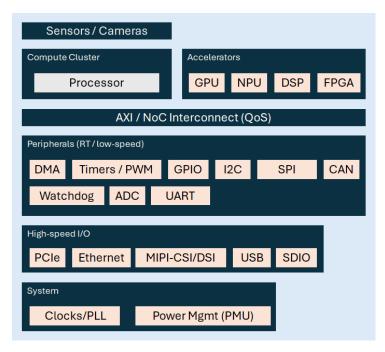

## SoC basics without the jargon

System on Chip (SOC) high level design

A System on Chip is a small city on a slice of silicon. You get a CPU for general work, a GPU or NPU for heavy math, memory blocks, and the streets that connect them called buses. Around that city sit the ports that touch the world. General purpose pins switch lights or read buttons. Converters turn voltages into numbers and back. Timers keep time. Interrupts wake the city when something important happens. Put it together and you have a computer that can sense, think, and act on its own.

Think in three layers. At the edge are signals you can touch. GPIO

flips digital inputs and outputs. ADC reads analog values like pressure or vibration. DAC writes analog values like a reference voltage. PWM creates precise pulses for motors and LEDs. Timers and counters measure durations and frequencies. Interrupts say stop what you are doing and look here. In the middle is data movement. Direct Memory Access moves blocks of data without bothering the CPU. Small shared buffers act like mailboxes between parts of the chip. At the core sits compute. The CPU runs control logic. The GPU or NPU crunches arrays for vision or language. Caches and formats decide how fast the math flows.

Why does this matter for graphs. Because an ONNX graph can run where the signals

originate. A camera feeds a stream into memory. DMA places frames without copies. The runtime reads tensors in place. The decision lands while the belt still moves. Latency drops because you do not ship data across a network. Energy drops because you do not spin big servers for tiny decisions. Portability holds because the same graph can target different SoCs through different providers while keeping the same logic.

Nvidia Jetson Orin SOC

Two pictures make it concrete. In a bottling line a

tiny board watches caps and fills. A sensor fires, a frame arrives, a model checks the meniscus, and a reject arm nudges a faulty bottle. The action happens in tens of milliseconds. In a smart street cabinet a board reads weather and traffic sensors, adjusts timing for a crossing, and reports summaries every minute. No one babysits the box. The graph is the script and the chip runs the play.

Keep a simple mental kit for SoCs.

- Signals: GPIO, ADC, DAC, PWM, timers, interrupts

- Movement: DMA, shared buffers, ring queues

- Compute: CPU for logic, GPU or NPU for arrays

- Wins: low latency, low energy, same logic on many boards

# State of the Art in Graph Computing and Hardware Orchestration (2021–2025)

#### Introduction

Graph-based computing has become a cornerstone of modern AI systems. Neural networks are naturally expressed as computational graphs where nodes represent operations and edges represent data flows (tensors). Beyond model inference, many AI workflows – from sensor acquisition to decision-making and actuation – can be modeled as dataflow graphs or directed acyclic graphs (DAGs). Representing workflows in this form enables global optimization, reproducibility, parallelism, and a unified view of the system.

Between 2021 and 2025, major advances have been made in graph compilers, distributed DAG schedulers, hardware-specific runtimes, and pipeline orchestrators. Yet, none of the existing approaches fully unifies **AI computation, orchestration logic, and hardware I/O** under a single portable artifact. This section surveys key academic and industrial efforts and highlights the gap that motivates the development of **ONNX GO HW**.

#### **Graph Compilers and Runtimes**

Modern compilers and runtimes transform computation graphs into optimized executables tailored to each hardware target.

- **ONNX Runtime (ORT)** A cross-platform engine for executing ONNX graphs with kernel fusion, memory planning, and multiple Execution Providers (CUDA, TensorRT, oneDNN, DirectML, OpenVINO, etc.). Widely used in production for portability and performance.

- **Apache TVM** An open-source compiler stack applying graph-level and tensor-level optimizations, including auto-scheduling (Ansor). Supports CPUs, GPUs, microcontrollers, and custom ASICs.

- Google XLA / MLIR A compiler infrastructure generating optimized HLO IR for CPUs, GPUs, and TPUs, excelling at static graph optimizations.

- **NVIDIA TensorRT** A high-performance runtime for NVIDIA GPUs, focused on inference, with aggressive optimizations (layer fusion, quantization).

- **Meta Glow** A graph-lowering compiler producing optimized code for heterogeneous devices, though with declining adoption compared to ORT/TVM.

**Strength:** excellent inference performance.

**Limitation:** focus on neural nets only; pre/post-processing, control flow, and hardware orchestration remain external.

## Pipeline Orchestration Frameworks

Some frameworks address end-to-end workflows by connecting models with other processing nodes.

- **NVIDIA Triton Inference Server** Supports ensembles of models connected as DAGs, with batching and scheduling. Optimized for serving at scale, not embedded control.

- NVIDIA Holoscan (GXF) Graph Execution Framework for real-time sensor/Al pipelines on Jetson/Orin. Provides zero-copy buffers and deterministic scheduling, but mainly tied to NVIDIA hardware.

- **NVIDIA DeepStream** A graph-driven multimedia pipeline framework based on GStreamer, targeting video analytics.

- ROS 2 Widely used in robotics, representing systems as graphs of nodes communicating via DDS. Strong for modularity, but determinism and real-time guarantees remain challenging.

- **LabVIEW** The precursor of visual graph-based programming, with native support for control and I/O. Historically limited by dependence on proprietary runtimes and lack of AI-native integration.

**Strength:** integration of multiple components (sensing, AI, control).

**Limitation:** models are often treated as black boxes; no unified graph artifact combining AI and I/O.

#### Hardware-Specific SDKs and DSLs

Vendors have created specialized graph-oriented SDKs to maximize performance on their chips.

- **AMD Vitis AI** Compiles models into FPGA DPUs, enabling efficient inference with quantization.

- Xilinx Adaptive Dataflow (ADF) DSL for programming Versal AI Engines as graphs of kernels and streams.

- Qualcomm QNN SDK Constructs hardware-specific graphs for Snapdragon SoCs, mapping to DSPs, NPUs, and GPUs.

- **NVIDIA CUDA Graphs** API to reduce GPU kernel launch overhead by chaining kernels as graphs.

- Intel oneAPI / OpenVINO Graph IRs optimized for Intel CPUs, GPUs, and VPUs.

**Strength:** hardware efficiency, near-ASIC performance.

**Limitation:** vendor lock-in; portability and orchestration across vendors not supported.

#### Limitations of the Current State of the Art

Despite the breadth of solutions, several gaps remain:

- 1. **Fragmentation** Inference engines, orchestrators, and hardware SDKs remain siloed, requiring glue code.

- 2. **No unified artifact** Al models, control loops, and I/O logic are spread across different runtimes.

- 3. **Vendor lock-in** Each hardware vendor exposes its own graph DSL, reducing portability.

- 4. **Lack of determinism** Few frameworks address real-time guarantees, safety profiles, or certifiability for aerospace/automotive/defense.

#### Transition to GO HW

These gaps open the path for **ONNX GO HW**:

- One graph artifact (ONNX) for computation, orchestration, and I/O.

- One runtime engine (ONNX Runtime) that schedules both math and hardware nodes.

- One **cockpit** (LabVIEW-style IDE) to author, configure, deploy, and monitor.

This unified approach is portable across vendors, auditable for safety-critical domains, and efficient for embedded deployment.

## Comparative Snapshot

| Framework<br>/ SDK       | Al Models              | Control Flow          | Hardware I/O                  | Portability                    | Real-Time / Safety            |

|--------------------------|------------------------|-----------------------|-------------------------------|--------------------------------|-------------------------------|

| ONNX<br>Runtime          | Yes                    | Limited<br>(If/Loop)  | No                            | High                           | Partial (fallbacks)           |

| Apache TVM               | Yes                    | No                    | No                            | High                           | No                            |

| TensorRT                 | Yes (GPU)              | No                    | No                            | NVIDIA-only                    | No                            |

| ROS 2                    | Yes (as external node) | Yes                   | Yes (via drivers)             | High                           | Limited determinism           |

| Holoscan /<br>DeepStream | Yes                    | Partial               | Yes (streams)                 | NVIDIA-only                    | Some deterministic scheduling |

| Vitis AI /<br>QNN / ADF  | Yes                    | No                    | Partial                       | Vendor-only                    | Limited                       |

| GO HW<br>(proposed)      | Yes                    | Yes<br>(If/Loop/Scan) | Yes (GPIO, DMA, ADC/DAC, PWM) | High (via Execution Providers) | Yes                           |

#### **Closing Sentence**

The fragmentation of today's tools highlights the need for a unified solution. **This gap** motivates GO HW, a concrete path from static description to dynamic technology.

# GO HW, a concrete path from static description to dynamic technology

**GO HW stands for Graph Orchestration for Hardware**. It turns a single ONNX graph into a living control loop that runs on real chips. The artifact stays ONNX. The engine stays ONNX Runtime. The cockpit stays LabVIEW. What changes is that hardware primitives become first-class nodes and timing becomes part of the plan.

Take the thought experiment and give it a name. GO HW is our way to turn ONNX from a static file into a living plan. ONNX stays the language that describes the graph. ONNX Runtime stays the engine that compiles and executes the plan. LabVIEW stays the cockpit where people think in graphs. GO is the glue that makes schedules, policies, and lifecycle first class citizens inside the same artifact.

The change is simple to feel. Instead of juggling scripts and private formats, teams keep one ONNX bundle that carries model structure, training logic when needed, evaluation flows, and housekeeping such as metrics and checkpoints. The runtime sees the whole plan, fuses what it can, sizes memory once, and delivers a session that behaves the same every time you call it. Reviews become graph diffs. Tests become graph runs. Rollbacks become file swaps.

We do not invent a new file or a new engine. We make better use of what exists. Control flow nodes like If, Loop, and Scan are not extras for edge cases. They are the handles that let you encode learning loops, curriculum choices, early stopping, and

reporting without leaving the ONNX world. The result is a clean pipeline that is portable, auditable, and friendly to both engineers and researchers.

**Ergonomics remains a first-class concern**. Layer mode gives practitioners the speed of Keras style building blocks. Node mode gives researchers fine control at the operator level. Both write to the same ONNX graph. Both compile to the same session. Both benefit from the same runtime optimizations. Your team chooses the view. The artifact stays one.

#### Three promises of GO HW

- One artifact for the lifecycle

- One engine for performance and portability

- One cockpit that makes graphs natural to author and reason about

#### GO HW on SoCs, author, configure, deploy, monitor

Think of GO HW as a four-step groove. You author a graph, you configure a target, you deploy a compiled plan, you monitor the run. Same artifact, same engine, different boards.

**Author.** Build the model as an ONNX graph in the LabVIEW cockpit. Engineers use layer blocks when they want speed. Researchers switch to node level when they want precision. Pre and post processing live in the same graph when it makes sense. Shapes, dtypes, and opset are checked early so the file is clean before you touch hardware.

**Configure.** Pick a board and load its device profile. The profile describes memory, supported providers, and practical limits such as how many concurrent streams make sense. The tool suggests a partitioning plan across providers. You confirm what runs on CPU, what runs on GPU or NPU, and what the Hardware EP will bind when hardware primitives are present. One click produces a plan you can review.

**Deploy.** ONNX Runtime compiles the graph into a session for that SoC. Kernels that fit together are fused. Memory arenas are sized to avoid hot path allocations. Formats are aligned so tensors do not ping pong between layouts. You ship a compact bundle that contains the graph, the compiled artifacts, and a small manifest. The device starts the session and keeps it resident.

**Monitor.** A tiny agent speaks gRPC for a side channel. Operators can read metrics, watch a few tensor taps, and adjust whitelisted parameters without touching the hot path. The session keeps its timing and memory stable. The agent handles logs, health checks, and safe restarts. You can stage a new graph, switch over, and roll back with short commands.

Here is a simple way to keep the loop healthy.

#### Happy path checklist

- Validate shapes and opset at author time

- Compile once per target and reuse the session

- Keep preprocessing and metrics in the graph when practical

- Track versions with a clean semantic tag and a short changelog

- Warm up the session after boot and record a baseline

A small example makes it real. A sorter runs on a Jetson today and moves to a Zynq board next quarter. You do not rewrite the logic. You open the same ONNX file, select a different device profile, compile for the new target, and deploy. ONNX Runtime picks the right providers. The agent reports the same metrics. Operations do not learn a new tool. They keep their eyes on the same cockpit.

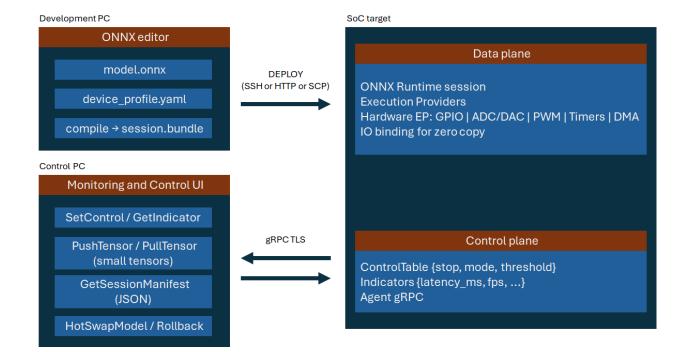

First functional architecture for GO HW

The model graph authored on the development PC is encapsulated as a subgraph within a larger control graph, wrapped in a Loop (while) node with a configurable cadence and an exit condition set in the editor.

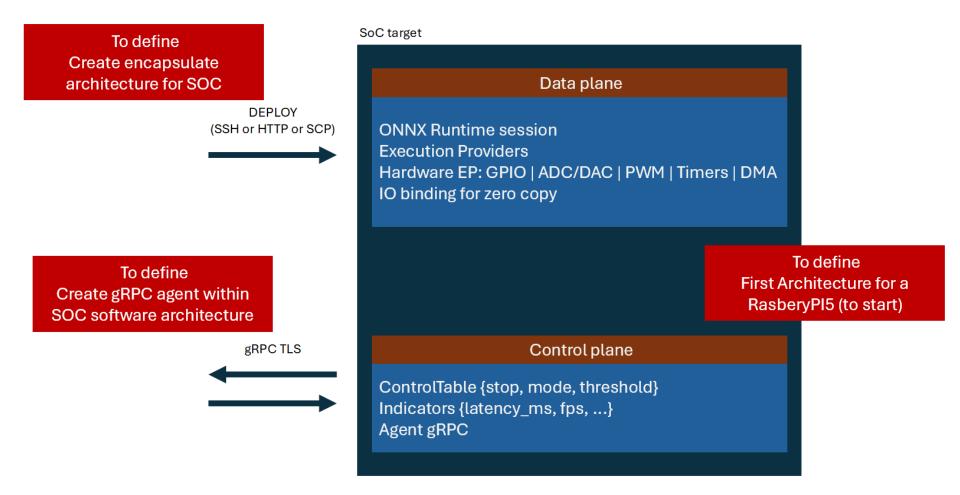

On the Development PC you work in the ONNX editor inside LabVIEW. You author the graph as model.onnx, pick a device\_profile.yaml for the target, then compile to a session.bundle. The bundle contains the optimized graph, the chosen Execution Providers, and the I O bindings the runtime will use. You deploy this bundle to the SoC over SSH or HTTP or SCP.

On the SoC target the data plane runs an ONNX Runtime session. Execution Providers accelerate subgraphs on the available engines. A Hardware EP exposes GPIO, ADC and DAC, PWM, timers and DMA as graph accessible services. I/O binding connects device or pinned buffers to inputs and outputs so tensors move without extra copies. Beside the data plane sits the control plane. It keeps a small ControlTable for parameters like stop, mode and threshold, an Indicators set for states like latency and fps, and a gRPC agent that exposes these knobs. The control plane never blocks the hot path. DMA is kept for large streams such as camera or audio, while small controls use local registers.

On the Control PC the Monitoring and Control UI speaks four simple verbs over gRPC with TLS. SetControl and GetIndicator write and read small parameters and states. PushTensor and PullTensor send or fetch small tensors through named bindings, useful for calibration or checks. GetSessionManifest returns a JSON snapshot of the active session with providers, partitions and I O bindings so you can inspect what runs where. HotSwapModel replaces the active bundle after validation and warmup, and Rollback restores the previous one if a health check fails.

This layout keeps one artifact, one engine and one cockpit. Today the LabVIEW loop still drives the session tick by tick, which makes debugging simple. Next we bring more schedule into the graph with If, Loop and Scan while keeping the same planes, the same API and the same zero copy path.

#### Proposed hardware nodes (first wave)

- sys.ControlGet(name) → read a small scalar/vector from the ControlTable (e.g., threshold, mode, stop).

- sys.IndicatorSet(name, value) → publish metrics/states (latency\_ms, fps, temperatures).

- sys.Clock(period | source) → provide ticks or timestamps to cadence a Loop.

- sys.TriggerIn(source) → edge or level trigger from external signal or timer.

- sys.Delay(ms | cycles) → bounded delay inside a control subgraph.

- sys.MetricTap(tensor, rate) → sample a tensor safely for monitoring without perturbing the hot path.

- sys.Watchdog(timeout\_ms, safe\_action) → enforce a safe state if timing budgets are missed.

- sys.SafeState(action) → explicit fallback action (e.g., de-energize outputs).

- hw.GPIOIn(pin) → boolean/u8 input; debouncing as attribute.

- hw.GPIOOut(pin, value) → digital output with optional pulse attributes.

- hw.ADCIn(chan, shape) → acquire analog samples into a tensor; sampling rate as attribute.

- hw.DACOut(chan, value) → write analog value; optional slew/limits.

- hw.PWMOut(chan, duty, freq) → generate PWM; jitter and range as attributes.

- hw.RTFifoDequeue(name) / hw.RTFifoEnqueue(name, tensor) → bounded realtime queues for small deterministic streams.

- hw.DMARead(channel, bytes|shape) → zero-copy intake from device to tensor (camera, ADC DMA).

- hw.DMAWrite(channel, tensor) → zero-copy out to device.

**Binding rules.** Controls/Indicators live in local RAM (small scalars). RT-FIFO for small deterministic streams. DMA is reserved for large flows. All bindings are **named handles** (no raw pointers) and appear in the session **manifest**.

Once a graph touches real pins, safety and evidence stop being optional. We introduce observability and device profiles so teams can trust what runs and prove it.

#### **Energy-Aware Graphs and Forensic Monitoring**

A missing cornerstone of today's AI deployment is energy. Performance metrics such as latency and accuracy dominate the discussion, yet energy – the joules consumed per inference or training step – remains invisible. GO HW enables users to explicitly elevate energy as a **scientific**, **reproducible metric** inside graph orchestration. Models can thus be evaluated not only for their predictions, but also for their execution cost, with energy becoming part of the same first-order evidence as accuracy or latency.

GO HW extends the monitoring plane with energy measurement. Each Execution Provider can expose an optional Energy Provider API to start and stop sampling during graph execution. Readings from hardware counters (e.g. NVML/PCAT for NVIDIA GPUs, RAPL for Intel CPUs, INA3221 for Jetson SoCs, PMBus for FPGA boards) are collected and normalized into joules per run. While these sources provide useful indicative values, they do not always reach **forensic-level precision**. To address this gap, Graiphic envisions building dedicated **test benches per hardware platform**, equipped with calibrated external instrumentation, and publishing the results openly in the same transparent manner as its Execution Providers Tester project. This approach ensures that hardware profiles are backed by auditable, high-precision evidence of energy consumption.

These measurements become **energy semantics**: annotations attached to nodes, subgraphs, or sessions, preserved in the Session Manifest. They enable reproducibility (same model, same joules), comparability (different boards, same metric), and accountability (evidence for audits and certification).

Beyond monitoring, GO HW introduces a **new family of loss functions where energy is a first-class component**. Users may define multi-objective optimization goals ( $L = \alpha * error + \beta * joules$ ), or construct custom losses directly from measured values by wiring hardware counter nodes into the training graph. This allows energy to be treated as a **standard optimization signal**, not merely as an external log. Graph-level optimizations such as kernel fusion, quantization, pruning, and early exit branches further reduce consumption without altering hardware.

By combining indicative monitoring, forensic test benches, semantic annotation, and energy-aware loss design, GO HW makes energy visible, actionable, and reproducible in AI systems deployed on real hardware.

#### LabVIEW-native forensic measurement.

A defining advantage of Graiphic's GO HW project is its native LabVIEW environment. LabVIEW has long been the gold standard in test and measurement, and this DNA translates directly into energy-aware AI orchestration. Beyond relying on low-level counters (temperature sensors, CPU utilization, or memory load), GO HW can leverage LabVIEW instrumentation to build rigorous test benches for each target SoC. These benches combine calibrated DAQ hardware with reproducible orchestration scripts, enabling precise measurements of joules consumed per model, per architecture, and per workload.

In practice, this means that GO HW can go beyond inference from indirect indicators and provide forensic-grade energy profiles. These results can be benchmarked systematically across Raspberry Pi, Jetson, Zynq, i.MX and industrial IPCs, then published openly on Graiphic's GitHub as reference datasets. By doing so, Graiphic not only monitors energy but sets a reproducible standard for the entire community, where performance is always reported together with energy consumption. This approach ensures transparency, comparability, and long-term credibility, aligning with DARPA's ambition to make energy a first-class scientific metric in machine learning.

#### Open benchmarking and transparent culture.

A key part of Graiphic's DNA is a culture of transparency and open collaboration. We systematically publish our benchmarks and tools on GitHub, not only to demonstrate capability but also to provide the community with actionable insights. A representative example is the <a href="Execution Providers Tester">Execution Providers Tester</a>, an open-source initiative that systematically maps ONNX Runtime operator coverage across all Execution Providers. This project, maintained as part of SOTA, has become a reference point for developers and vendors to understand backend support, prioritize missing operators, and track reproducibility across environments.

We apply the same philosophy to energy. With GO HW, our goal is to build and publish forensic-grade energy benchmarks per SoC, validated with LabVIEW-native test benches and external instrumentation. These results will be openly shared on Graiphic's GitHub, in the same transparent manner as our operator coverage tester. By doing so, Graiphic not only demonstrates mastery of the entire ONNX stack, from operators to orchestration to hardware execution, but also provides the ecosystem with clear, reproducible metrics and actionable objectives. This open benchmarking culture ensures trust, comparability, and alignment with DARPA's emphasis on scientific rigor.

## Algorithmic Enhancements: Dynamic Loss Functions and Informed Learning through Full Graph Orchestration

#### Dynamic, energy-aware loss design.

Unlike conventional frameworks where loss functions are hard coded into the training loop, GO HW, built on Graiphic's SOTA orchestration layer, treats the loss as a first-class graph component. This enables the injection of dynamic loss subgraphs at runtime, blending traditional accuracy-driven objectives with hardware-derived energy metrics exposed via new HW nodes such as GPIO, DMA, timers, ADC/DAC, and power counters. Losses can therefore explicitly minimize both prediction error and joules consumed. For example:  $L = \alpha \times error + \beta \times energy$

This capability is unique. SOTA is currently the only framework that can dynamically orchestrate and reconfigure such hybrid objectives directly inside the ONNX graph, making energy optimization a native part of the training loop rather than an afterthought.

#### Graph-compilation efficiency as orchestration property.

GO HW leverages ONNX Runtime Execution Providers, which means that every graph passes through optimization pipelines where redundant operations are removed and compatible nodes are fused into efficient kernels. What differentiates Graiphic's approach is that these compiler-level passes are orchestrated, inspected, and controlled at the graph level. Energy gains are no longer incidental side effects of compilation; they are visible, reproducible orchestration choices. Only a framework with full graph mastery such as SOTA can expose and standardize this capability.

#### Integration of alternative learning paradigms.

Through its orchestration-first architecture, GO HW seamlessly integrates self-supervised and informed learning approaches as native graph constructs. In self-supervised learning, contrastive vision methods such as SimCLR have exceeded supervised ImageNet performance with 100 times fewer labels, while in NLP masked token prediction achieves state-of-the-art results with minimal annotation. In informed learning, domain constraints and physical laws are encoded directly into the optimization graph. Zhang et al. (2021) demonstrated that an elastic-energy-constrained network matched supervised accuracy without ground-truth data. In computational fluid dynamics, informed networks reproduced full simulations approximately 60 times faster than FEM or FVM solvers. In structural engineering, PINNs incorporating conservation laws provided more precise stress predictions while reducing computational cost. These paradigms converge faster, require fewer epochs, and consume significantly less energy. With GO HW's orchestration layer, they become deployable as graph-native strategies rather than external workarounds.

#### Impact: Green AI by design.

By uniting dynamic energy-aware losses, orchestrated compiler optimizations, and alternative ML paradigms, GO HW transforms energy from a passive metric into an active design variable. This positions Graiphic's SOTA as the only fully orchestrated graph framework able to embed energy directly into learning, ensuring AI systems that are not only accurate but also efficient, reproducible, and sustainable.

## Energy-aware contributions of SOTA and GO HW

| Category                                     | SOTA contributions                                                                                                                                                                                                                                                                                                                                                                                                                             | GO HW contributions                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Prevention<br>(reduce energy<br>upfront)     | <ul> <li>Graph orchestration allows dynamic injection of energy-aware loss functions.</li> <li>Operator fusion, pruning, quantization embedded at graph level.</li> <li>Support for alternative paradigms (self-supervised, informed ML) reducing training epochs and data labeling effort.</li> <li>Training orchestration inside ONNX graphs (loss, optimizer, control flow) avoids scattered scripts, ensuring leaner execution.</li> </ul> | <ul> <li>Hardware primitives (GPIO, DMA, timers, ADC/DAC) exposed as nodes, enabling energy-aware design directly tied to SoC resources.</li> <li>Cross-hardware portability (CPU, GPU, FPGA, SoC) allows selecting the most energy-efficient target.</li> <li>Automatic graph compilation with kernel fusion and memory planning across Execution Providers to reduce wasted cycles.</li> </ul>                  |  |  |

| Monitoring<br>(measure and<br>expose energy) | <ul> <li>Native LabVIEW environment provides intrinsic test &amp; measurement DNA.</li> <li>Session manifests and metrics are integrated into orchestration layers for reproducible runs.</li> <li>Early monitoring hooks for latency, memory, and resource usage.</li> </ul>                                                                                                                                                                  | Forensic-grade energy monitoring via Execution Providers extended with Energy Provider APIs (NVML, RAPL, INA3221, PMBus).  Dedicated LabVIEW test benches with calibrated DAQ for per-SoC joule measurement.  Energy semantics preserved as annotations in Session Manifest.  Open GitHub culture: publishing per-model/per-architecture benchmarks for transparency (e.g. Execution Providers Tester precedent). |  |  |

| Curation<br>(optimize after<br>deployment)   | <ul> <li>Ability to re-train or fine-tune models by dynamically adjusting losses including energy terms.</li> <li>Graph-level rewrites (kernel fusion, pruning, early exits) as corrective strategies.</li> <li>Switch between inference/training/academic sessions for flexible post-hoc tuning.</li> </ul>                                                                                                                                   | <ul> <li>Migration of trained models across hardware (GPU → FPGA/SoC) to achieve better energy/performance trade-offs.</li> <li>Hot-swap and rollback mechanisms in deployed sessions without breaking timing or safety constraints.</li> <li>Multi-objective optimization functions (error + joules) guiding iterative refinement of deployed systems.</li> </ul>                                                |  |  |

## Closing, one graph, many roles

The path is simple to state. Keep one artifact. Let it describe models, training schedules, and workflows. Run it with one engine across many devices. Give people a cockpit that feels natural. This is how ONNX, ONNX Runtime, and the LabVIEW experience come together in GO HW.

What changes for teams is focus. You spend less time stitching scripts and more time shaping graphs. You review optimized graphs like code. You move the same file from experiment to evaluation to deployment. You target a workstation, a Jetson, a Zynq, or a PC, and the logic stays the same. You gain speed because the runtime plans the work. You gain trust because the plan is visible.

What changes for the ecosystem is reach. A native ONNX editor removes the dependency on third party export paths. Control flow nodes become everyday tools instead of hidden features. The SONNX safety profile gives sensitive sectors a clear contract for meaning and evidence. ONNX grows from an excellent file format to a complete graph computing framework that spans learning, serving, and control.

# Implementation and Deployment of ONNX GO HW on SoCs (Raspberry Pi 5 as First Case Study)

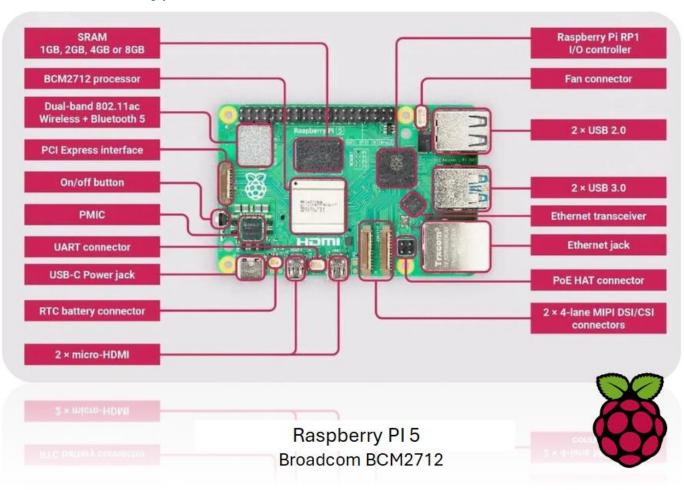

The implementation of ONNX GO HW follows a structured workflow, moving from operator specification to deployment and monitoring on real SoCs. We start with the **Raspberry Pi 5** (Figure 0) as the initial demonstrator. Based on the **Broadcom BCM2712**, this board provides a rich set of interfaces (USB, Ethernet, GPIO, PCIe, etc.), making it an ideal target to define and validate the initial architecture.

#### **∳**GRAIPHIC

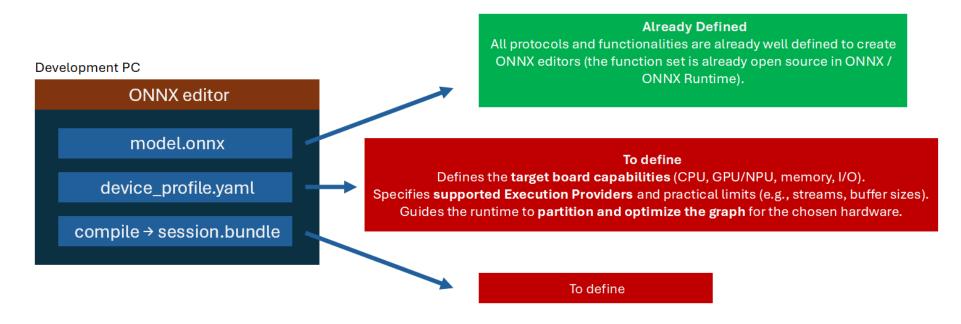

On the development side, three core artifacts are essential:

- model.onnx: the graph definition, representing the universal contract.

- device\_profile.yaml: the SoC "identity card," describing available resources (CPU, GPU/NPU, memory, I/O) and constraints.

- **session.bundle**: the optimized execution package ready for deployment on the target.

These artifacts build on existing ONNX / ONNX Runtime mechanisms, ensuring interoperability and standardization.

#### **∳**GRAIPHIC

A first proof-of-concept is already visible in the LabVIEW **Graiphic IDE**, which demonstrates that custom development environments can be constructed directly from the open-source ONNX toolchain. This highlights the possibility for third-party IDEs to leverage the same functional core.

The development workflow can be divided into two categories:

- 1. Already defined by ONNX (graph compilation, operator schemas, execution management).

- 2. **To be specified** (hardware node encapsulation, standardized SoC profiles).

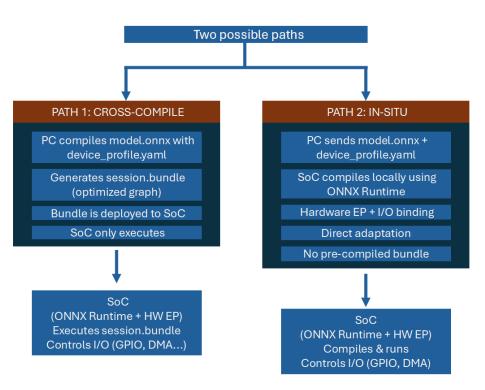

At deployment time, two execution scenarios are possible:

- **Cross-Compilation**: the graph is compiled on the development PC using the target profile, producing an optimized **session.bundle** that is transferred to the SoC. Advantage: simulation can be performed before deployment.

- In-situ Compilation: the PC sends the model and profile, and ONNX Runtime compiles directly on the SoC, adapting natively to available hardware resources.

Once deployed, the architecture runs inside the **SoC execution environment** (Figure 5):

- **Data Plane**: ONNX Runtime session extended with Hardware Execution Providers (GPIO, ADC/DAC, PWM, DMA, etc.), using optimized memory bindings for zero-copy execution.

- **Control Plane**: runtime configuration via a control table (start/stop, thresholds, modes), performance indicators (latency, FPS, metrics), and a gRPC-based agent ensuring monitoring, remote access, and execution safety.

#### **∳**GRAIPHIC

Finally, the **supervision layer** establishes secure communication via gRPC TLS between the **Control PC** and the SoC. It exposes a standardized set of functions: configuration and indicator retrieval, small tensor transfers, access to the session manifest (JSON), and dynamic model lifecycle management (HotSwap/Rollback).

#### Conclusion

Demonstrating this workflow on Raspberry Pi 5 will provide the first **end-to-end validation** of ONNX GO HW, proving that ONNX can orchestrate SoC-level resources through an optional hardware namespace. From this initial feasibility study, the experience gained will drive:

- standardization of SoC profiles and hardware nodes,

- Progressive extension to additional platforms (Jetson, Zynq, FPGA, i.MX, etc.),

- reproducibility through portable device\_profile.yaml descriptions and unified functions.

This approach ensures that each new SoC can be integrated into the ONNX GO HW ecosystem through the addition of a profile in a shared library, guaranteeing interoperability, portability, and long-term adoption.

#### Proposed Path Forward for ONNX steering committee

To ensure clarity and avoid fragmentation, we propose the creation of an **experimental optional domain** under ONNX, tentatively named **onnx.hardware**.

- **Status**: The operators defined in this domain would be *optional*, exactly like other ONNX operators that are not universally implemented across Execution Providers. No vendor would be required to support them.

- **Scope**: Initial focus on SoC primitives such as GPIO, DMA transfers, ADC/DAC, timers, and synchronization nodes.

- Deliverables:

- 1. Draft operator definitions with schemas and documentation.

- 2. Mapping tables to existing vendor APIs (e.g., CUDA, DAQmx, XRT, OpenVINO, oneAPI).

- 3. An open-source prototype (starting with Raspberry Pi 5) demonstrating feasibility.

- Governance: This domain would be managed under a new ONNX Hardware Working Group, working in coordination with existing WGs (e.g., Multi-Device, Generative AI).

- **Goal**: Provide a recognized namespace where hardware orchestration operators can be incubated in a structured way, ensuring legitimacy, community visibility, and long-term alignment with the ONNX standard.

This approach guarantees that ONNX remains lightweight at its core while providing a credible framework for vendors and industrial adopters who wish to expose hardware-level capabilities within ONNX graphs.

Creating a dedicated ONNX Hardware Working Group is not just an implementation detail, it is a strategic step to ensure ONNX remains the common, extensible, and trustworthy foundation for real-world deployment on hardware, beyond inference.

#### Why ONNX Needs a Hardware Working Group, Strategic Rationale

Creating an ONNX Hardware Working Group is not just a technical proposal. It is a strategic move to ensure ONNX evolves with the needs of its community, expands its scope, and maintains its leadership in the AI ecosystem. Below are eleven key reasons why this effort is essential:

- Expand ONNX beyond inference GO HW transforms ONNX from a simple inference format into a full orchestration framework. This enables use cases in control, automation, edge AI, and closed-loop systems, far beyond static prediction tasks.

- 2. **Meet rising demand for edge and SoC deployments** Many industrial and embedded applications require tight integration between compute and I/O. By supporting primitives such as GPIO, DMA, ADC, and PWM, ONNX becomes relevant for real-world deployments on low-power, timing-sensitive hardware.

- 3. **Prevent fragmentation through standardization** Without an official hardware namespace, vendors will create their own incompatible extensions. A dedicated working group ensures that hardware-related nodes and behaviors are defined in a consistent, interoperable, and open way.

- 4. **Enable portability and reproducibility across devices** With standardized hardware nodes and profiles, the same ONNX graph can be deployed to a Raspberry Pi, Jetson, or Zynq board without rewriting logic. This simplifies testing, integration, and reuse across heterogeneous targets.

- 5. Support safety-critical applications with auditability and trust A hardware domain aligned with the SONNX Safety Profile enables certification and traceability in regulated sectors such as aerospace, defense, healthcare, and automotive. This elevates ONNX from an experimental tool to a trusted platform.

- 6. **Support real-time orchestration and deterministic control** ONNX already includes control-flow nodes like Loop, If, and Scan. Combined with hardware-timed operations, these allow ONNX graphs to express scheduling, triggering, and timing constraints essential for modern automation and robotics.

- 7. **Anchor long-term evolution with clear governance** A working group provides legitimacy, shared ownership, and a structured path for future development. It ensures that hardware orchestration capabilities evolve under community guidance and remain aligned with the ONNX roadmap.

- 8. **Evolve ONNX into a complete, standalone platform** Currently, ONNX acts as an exchange format dependent on third-party toolchains. By introducing native graph editing and execution orchestration, ONNX can become a first-class platform for authoring, deploying, and managing graph-based applications directly.

- 9. Adapt to emerging technological needs and open new domains Supporting hardware and orchestration opens the door to new use cases in industrial Al,

robotics, embedded systems, and cyber-physical infrastructure. It also brings new contributors from fields beyond machine learning, such as control engineering and systems design.

- 10. Avoid losing relevance to emerging standards If ONNX does not address hardware orchestration, another format eventually will. The demand is real and growing. Leaving this space unaddressed creates a risk of fragmentation or replacement, potentially rendering ONNX obsolete in key domains.

- 11. Demonstrate vitality and attract innovation A dynamic ecosystem attracts researchers, engineers, and academics. Supporting this initiative sends a clear signal that ONNX is open to innovation, collaborative, and responsive to real-world needs. Refusing to engage could suggest stagnation or retreat, harming the long-term health of the project.

The Artemis rover could run on ONNX. We just have to make that choice.

Here is a short list of actions that make the vision concrete.

#### Calls to action

## For the ONNX community

- Define standard hardware nodes: hw.GPIOIn, hw.GPIOOut, hw.ADCIn, hw.DACOut, hw.PWMOut, hw.RTFifoEnqueue/Dequeue, hw.DMARead/Write, sys.Clock, sys.TriggerIn, sys.Delay.

- Grow the Safety-Related Profile (SONNX) with reference tests and a profile interpreter

- Make timing budgets, watchdogs, and safe states first-class and verifiable.

- Standardize a Register abstraction Add a typed, named Register class for runtime get/set. Registers are small scalars or short vectors declared in a Control Table, with dtype, shape, default, access policy, update rate, and scope. Provide ONNX nodes sys.RegisterRead(name) and sys.RegisterWrite(name, value), plus editor annotations.

- Standardize a Session Manifest and a Session Log Manifest (JSON) at compile time: graph\_hash, opset, providers, device\_profile\_id, io\_bindings, register\_map (names, logical handles or offsets, types), taps, rt\_constraints.

- Log (NDJSON) at runtime: timestamped events, node ids, metrics, errors, and stable handles. No raw pointers by default; allow an explicit debug mode that adds physical addresses for low-level bring-up.

- Support a native ONNX editor that covers import, edit, and create

One artifact, less glue code, better auditability.

## For industry partners

- Publish device profiles for real boards in practical terms

GPIO counts and specs, ADC ranges and rates, FIFO and DMA sizes, memory layout, supported providers, known timing limits.

- Validate a "Pi to Any SoC" reference path with public metrics

Same graph across boards, reporting p50 and p99 latency, jitter, throughput, and energy.

- Ship minimal driver shims for hardware nodes and registers

Clean mappings to MMIO, sysfs, libgpiod, UIO, or char devices. Expose the register map through the Hardware EP and the agent.

- Provide ready-to-flash images and sample graphs

Reproducible day-one experience.

## For teams adopting GO HW

- Treat the ONNX file as the single source of truth

Version it and generate everything else from it.

- Keep preprocessing and metrics in the graph when practical Improves reproducibility and portability.

- Compile once per target and reuse sessions for stable timing Preallocate, warm up, and keep sessions resident.

- Use Registers for safe live tuning and monitoring

Clear names, bounded values, agent-side validation and ACLs. Prefer handles over raw addresses; enable debug mode only on bench rigs.

- Enable Manifest and Log with the right level

Verbose in dev, minimal in prod, alert on thresholds.